Как память нового поколения – DDR5 – меняет вещи?

От дополненной реальности до искусственного интеллекта, облачных вычислений до интернета вещей, 5G подпитывает рост новых технологий – и данных, которые они создают. С увеличением количества данных возникает необходимость в хранении и быстром доступе, что означает, что такая технология, как DDR5, никогда не была более важной. Потребность центров обработки данных в постоянном хранении, передаче и обработке этих данных раздвигает границы высокоскоростной сигнализации и приводит к испытаниям, которых до сих пор не было в памяти.

Что изменилось?

Оперативная память пятого поколения DDR5 сильно отличается от DDR4, которую можно купить в интернет-магазине 220.lv, и на самом деле больше похож на LPDDR4. Проверьте эти девять изменений, которые DDR5 приносит на стол:

- Это быстрее! Прежде всего, скорость передачи данных увеличивается до 6,4 Гбит/с, тогда как DDR4 остановился на 3,2 Гбит/с. В спецификации также предусмотрено, что в ближайшие годы ограничение скорости превысит 8 Гбит/с. Структура канала аналогична LPDDR4, где у нас есть два независимых 40 — битных канала с ECC. У нас также есть более высокая предварительная выборка, более высокая длина пакета и увеличенные банковские группы. Это все для повышения эффективности и включения высокоскоростных режимов..

- Еще одно большое изменение в DDR5 заключается в том, что записи не выровнены по центру. Существует фиксированное смещение между DQS и DQ. Это означает, что мы не можем просто измерить задержку между DQS и DQ в области видимости и выяснить, является ли это чтением или записью. Эта роскошь ушла. Разделение пакетов чтения и записи будет более сложным..

- Новые измерения джиттера часов. DDR5 вводит измерения Rj, Dj и Tj вместо измерений периода и цикла к циклу джиттера. Спецификации Rj очень жесткие при максимальной скорости передачи данных. Хорошая целостность сигнала будет иметь первостепенное значение для уверенного измерения этих параметров.

- Деэмбедирование будет иметь решающее значение при более высоких скоростях передачи данных DDR5. Де-встраивание — это метод удаления нагрузки зонда и интерпозера. Он также используется для виртуального перемещения точки зонда с шара DRAM на кристалл DRAM, чтобы минимизировать отражения. Мы хотим видеть то, что видит Rx. Для успешного создания файлов фильтра извлечения или функции передачи требуются файлы s-par — их много. Идея состоит в том, чтобы как можно точнее имитировать канал DDR, используя модели s-par для пакета SOC, моделей плат, пакета DRAM, интерпозеров, зондов, а также настройки ввода-вывода, такие как мощность привода Tx и ODT Rx (если применимо). В отсутствие моделей s-par можно также использовать простые параметры линии передачи, такие как задержка распространения и волновое сопротивление, путем измерения отражения на экране прицела.

- Впервые в ресивере будет эквализация Rx, 4-Tap DFE . Увеличение скорости передачи данных в DDR5 достигается без перевода шины DQ на дифференциальную передачу сигналов, т.е. шина DQ по-прежнему несимметрична, как и DDR3/4. Однако в канале памяти имеется множество точек с несовпадением импеданса, что увеличивает общую межсимвольную интерференцию из-за отражений. Ожидается, что при скоростях передачи данных выше 4800 Мбит/с глаз данных на шарике DRAM будет закрыт. DFE DFE с 4 отводами реализован в DDR5 DRAM Rx, чтобы помочь выровнять сигналы DQ и открыть глазки данных после того, как данные будут зафиксированы приемником. Кроме того, CA Rx RCD также потребуется DFE для обеспечения надежного захвата сигнала.

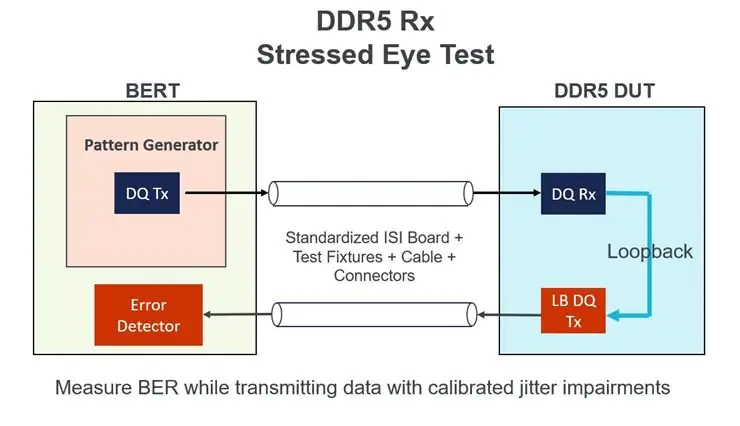

- Еще одним существенным изменением для DDR5 является включение обратного канала. Если вы посмотрите на карту контактов DDR5, вы найдете выделенные контакты обратной петли DQS/DQ. Это будет использоваться для включения автономной характеристики DRAM RX/TX. Петлевой обратный канал имеет решающее значение. Фактически, именно так мы узнаем, какое битовое решение принимает приемник в реальном времени. Это один провод, который используется всеми разными приемниками, и поскольку он имеет плохую целостность сигнала и по этой и другим причинам, именно поэтому мы отправляем обратно только каждый четвертый бит или каждый второй бит, так что у нас достаточно времени, чтобы иметь возможность убедитесь, что внешний приемник или детектор битовых ошибок могут со 100% точностью проверить качество встроенного Rx.

- Существует потребность в автономном тестировании DRAM Rx/Tx в DDR5 с использованием BERT и/или гибкого генератора шаблонов . Это открывает совершенно новый набор тестов, включая тесты на чувствительность к напряжению и частоте и тесты на нагрузку глаз, которых не было в DDR3/4. Концепция проста — любой должен иметь возможность использовать стандартизированное устройство JEDEC, следовать установленной JEDEC процедуре тестирования и выполнять стандартные тесты для определения работоспособности DRAM Rx/TX.

- Точная калибровка напряжения будет большой проблемой при тестировании DDR5 RX, и это получение точных моделей S-параметров, которые вам придется оценивать, а также измерять для всех сегментов. Еще одной важной особенностью будет возможность делать точные или хорошие предположения о глубине измерений и размерах записей осциллографа, чтобы вы не тратили слишком много времени.

- Тестирование DRAM Rx/Tx представит огромную проблему управления базами данных. Автоматизация и управление огромным количеством файлов s-par, моделей де-встраивания и результатов измерений станет кошмаром. Представьте себе тестирование 80+ контактов на разных скоростях для нескольких конфигураций DIMM от разных поставщиков. Это будет очень, очень сложно.

По сравнению с DDR3/4, DDR5 улучшает пропускную способность, плотность и эффективность канала. Но более высокие скорости передачи данных и более высокие скорости передачи сигналов требуют более высоких показателей производительности для соответствия требованиям, отладки и проверки. Понимание различий, присущих DDR5, может помочь в эффективной проверке и отладке.

Редактор: AndreyEx