4-битный Сумматор-вычитатель

4-разрядный сумматор-вычитатель представляет собой цифровую схему, способную выполнять арифметические операции с двоичными числами длиной в четыре бита. Используя продуманную комбинацию логических элементов и триггеров, эта универсальная схема способна складывать или вычитать два 4-разрядных двоичных числа с замечательной эффективностью и точностью.

В этой статье мы углубляемся во внутреннюю работу 4-разрядного сумматора-вычитателя, исследуя его архитектуру, логическую реализацию и приложения. Мы рассмотрим, как этой компактной схемотехнике удается обеспечивать функции сложения и вычитания в лаконичном корпусе, что делает ее бесценным компонентом в широком спектре цифровых систем.

Что такое двоичный сумматор и вычитающее устройство?

В сфере цифровых схем двоичный сумматор-вычитатель становится замечательным компонентом, который органично сочетает функции сложения и вычитания в рамках одной схемы. Его режим работы определяется двоичным значением, хранящимся в управляющем сигнале, что позволяет ему выполнять обе арифметические операции с максимальной эффективностью. Эта универсальная схема занимает важное место в качестве жизненно важного элемента арифметико-логического блока (ALU), основного компонента в различных вычислительных системах.

Для этой схемы требуется предварительное понимание элемента Exor, двоичного сложения и вычитания, а также полного сумматора.

В качестве входных данных цифровой схемы для операции с цифрами возьмем два 4-разрядных двоичных значения, A и B.

A0 A1 A2 A3 для A

B0 B1 B2 B3 для B

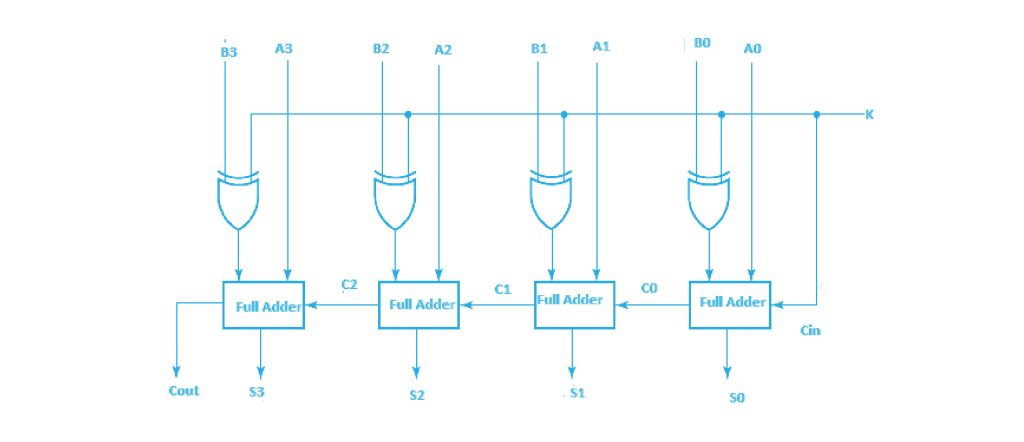

Поскольку мы работаем с 4-разрядными числами, схема состоит из 4 полных сумматоров. Существует управляющая строка K, которая имеет двоичное значение либо 0, либо 1, в зависимости от того, выполняется ли сложение или вычитание.

Входной сигнал Cin первого полного сумматора, который изображен на рисунке, является управляющей строкой. Входной сигнал A0, или младший значащий бит A, вводится непосредственно в полный сумматор. Exor из B0 и K служит третьим входом. Два выхода — перенос (C0) и сумма / разность (S0).

Если K (управляющая строка) имеет значение 1, то B0(exor)K=B0′(Complement B0). Следовательно, формула будет A+(B0′). A+B’+Cin теперь равняется дополнительному вычитанию двух чисел A и B. Это показывает, что четырехразрядные значения обрабатываются путем вычитания, когда K = 1.

Аналогично в случае, когда K=0, B0 (exor) K=B0. A + B — простая процедура двоичного сложения. Это означает, что операция также применяется к четырехразрядным числам, когда K = 0.

Затем второй полный сумматор принимает C0 в последовательной форме в качестве одного из своих выходных данных. Наименее важная часть суммы / разности записывается как сумма/различие S0. Прямыми входными данными для второго, третьего и четвертого полных сумматоров являются A1, A2 и A3. Затем значения B1, B2, B3 и K вычисляются вторым, третьим и четвертым полными сумматорами соответственно на третьем входе. Последовательный полный сумматор принимает сигналы переноса C1, C2 последовательно в качестве одного из своих входов. Полный перенос суммы / разности изменяется на C3. S0 добавляется к S1, S2, S3, и результат записывается.

Мы используем n полных сумматоров для создания n-разрядного двоичного сумматора-вычитателя.

Пример 4-битного сумматора и вычитателя

Предположим, что мы собираемся ввести два 3-разрядных значения в полный сумматор, X = 100 и Y = 011.

X0 = 0 X1 = 0 X2 = 1

Y0 = 1 Y1 = 1 & Y2 = 0

Для K= 0:

Y0⨁ K = Y0 и Cin = K= 0

Итак, из первого полного сумматора

S0 = X0 + Y0 + Cin

S0= 0+1+0

S0=1

C0=0

Аналогично,

S1 = X1 + Y1 + C0

S1 = 0+1+0

S1 = 1 и C1 = 0

Аналогично,

S2 = X2 + Y2 + C1

S2 = 1+0+0

S2 = 1 и C2 = 0

Таким образом,

X = 100 =4

Y = 011 = 3

Сумма = 0111 = 7

Для K = 1

Y0⨁K = Y0′ и Cin=k= 1

Итак,

S0 = X0 + Y0’+ Cin

S0 = 0+0+1

S0=1 и C0 =0

Аналогично,

S1 = X1 + Y1’ +C0

S1 = 0+0+0

S1=0 и C1=0

Аналогично,

S2 = X2 + Y2’ + C1

S2 = 1+1+0

S2 = 0 и C2 =0

Таким образом,

X = 010 = 4

Y = 011 = 3

Разница = 001 = 1

Вывод

4-разрядный сумматор-вычитатель является свидетельством простоты проектирования цифровых схем. Благодаря оригинальному сочетанию логических элементов и триггеров эта компактная схема обеспечивает исключительную производительность при выполнении арифметических операций с 4-разрядными двоичными числами. Как мы рассмотрели в этой статье, 4-разрядный сумматор-вычитатель предлагает функции как сложения, так и вычитания, обеспечивая универсальное решение для широкого спектра приложений.

Понимание внутренней работы 4-разрядного сумматора-вычитателя позволило выявить фундаментальные концепции двоичной арифметики и то, как они эффективно реализованы в этой схеме. Изучив его архитектуру и логическую реализацию, мы получили представление о различных методологиях проектирования и компромиссах, связанных с достижением оптимальной производительности.

Часто задаваемые вопросы: 4-разрядный сумматор и вычитатель

Вопрос 1: Что такое 4-разрядный сумматор и вычитающее устройство?

4-разрядный сумматор-вычитатель представляет собой цифровую схему, которая выполняет операции сложения и вычитания двоичных чисел, состоящих из четырех битов. Он объединяет функциональность сумматора и вычитающего устройства в одной схеме, позволяя выполнять эффективные арифметические вычисления.

Вопрос 2: Как работает 4-разрядный сумматор и вычитающее устройство?

Схема использует комбинацию логических элементов и триггеров для выполнения сложения и вычитания. В качестве входных данных принимает два 4-разрядных двоичных числа вместе с управляющим сигналом, который определяет подлежащую выполнению операцию (сложение или вычитание). Схема выполняет соответствующую операцию на основе управляющего сигнала, используя принципы двоичной арифметики и механизмы переноса / заимствования.

Вопрос 3: Каковы ключевые компоненты 4-разрядного сумматора и вычитателя?

4-разрядный сумматор-вычитатель обычно состоит из четырех полных сумматоров, которые соединены между собой для обработки сложения или вычитания отдельных битов. Дополнительно включены мультиплексоры или управляющие элементы для управления потоком данных и выбора желаемой операции.

Вопрос 4: Каковы области применения 4-разрядного сумматора и вычитающего устройства?

4-разрядный сумматор и вычитающее устройство находят применение в различных цифровых системах, таких как арифметические калькуляторы, микропроцессоры, цифровые сигнальные процессоры и блоки управления. Они необходимы для точного и эффективного выполнения арифметических вычислений в этих системах.

Вопрос 5: Могут ли 4-разрядный сумматор и вычитающее устройство обрабатывать большие числа?

Нет, 4-разрядный сумматор и вычитающее устройство могут обрабатывать только двоичные числа, состоящие из четырех битов. Для больших чисел необходимо каскадирование нескольких 4-разрядных сумматоров или использование схем сумматор-вычитатель с более высоким разрядом.

Редактор: AndreyEx