AMD предоставляет больше информации о 3D-стеке на Hot Chips 33

Вернувшись на Computex в июне, AMD завершила свой основной доклад очень интересным сегментом, в котором она представила прототип процессора Ryzen 9 5900X с добавленным 3D V-Cache. Мы узнали, что этот прототип стал результатом первой практической реализации AMD технологии стекирования чипов 3D. Фирма нацелена на кеш-память ЦП для этой модификации, поскольку было ясно, что это принесет немедленную выгоду для нескольких рабочих нагрузок.

Слайды, представленные на Computex, показали, что прототип с улучшенным 3D V-Cache обеспечивает в среднем на 15% более быстрый игровой процесс благодаря значительному увеличению пропускной способности, когда на каждую ПЗС-матрицу с использованием предоставленных TSV помещается 64-мегабайтная 7-нанометровая SRAM. Генеральный директор AMD д-р Лиза Су заявила, что первые процессоры Ryzen высокого класса, использующие 3D V-Cache, поступят в массовое производство в четвертом квартале этого года.

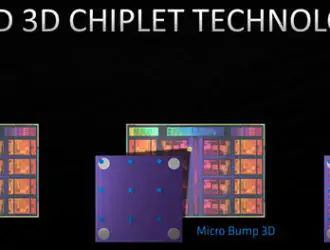

На Hot Chips 33 AMD представила дополнительную информацию об использовании технологии 3D-упаковки в будущих процессорах. ComputerBase опубликовала рецензию и обширную подборку слайдов из презентации AMD. Выше вы можете видеть, что соединения TSV, используемые AMD для подключения к 3D V-Cache, намного плотнее, чем предлагают предыдущие/конкурирующие технологии.

AMD сосредотачивает свои сравнения на микровыступах в трехмерном межкристальном соединении, которое намного грубее (в 15 раз меньше плотности), требует в 3 раза большей мощности межсоединений и страдает от более низких характеристик емкости и индуктивности.

Выше вы можете видеть, что AMD может похвастаться шагом 9u, который намного плотнее, чем микровыступы, или даже технология Intel Foveros Omni с шагом 36u. Однако в 2023 году Intel собирается начать создавать чипы Foveros Direct с шагом <10u.

AMD также тесно сотрудничает с партнером TSMC над более продвинутыми и сложными технологиями трехмерного стекирования. Тем не менее, это дает понять, что, хотя модульная конструкция — это путь вперед, не все типы микросхем выигрывают от одних и тех же стратегий трехмерной упаковки. Как поясняется на слайде выше, оптимальный выбор должен основываться на PPAC (мощность, производительность, площадь и стоимость).

Утечка платформы AMD AM5

Документы, которые просочились в результате недавней хакерской атаки Gigabyte, стали причиной появления нескольких технических статей в последние дни. Блок-схема сокета/чипсета AM5 была в центре внимания TechPowerUp в пятницу. Это показывает, что платформа будет поддерживать двухканальную DDR5, но будет ограничена PCIe 4.0.

В частности, платформы AM5 будут поддерживать 28 линий PCI-Express Gen 4. «16 из них выделены для дискретной графики PCI-Express, 4 — для подключенного к процессору слота M.2 NVMe, еще 4 — для дискретного контроллера USB4, а оставшиеся 4 — для шины набора микросхем», — сообщает TPU.

AMD перешла на PCIe 4.0 более чем на год раньше, чем Intel со своими настольными процессорами Rocket Lake, поэтому интересно наблюдать, как AMD уступает лидерство по PCIe 5.0 Intel. Intel уже подтвердила, что ее материнские платы Alder Lake-S будут поддерживать DDR4 или DDR5, в зависимости от платы, которую вы покупаете. Предстоящая платформа Intel для настольных ПК также будет поддерживать до 16 линий PCIe 5 и ряд линий PCIe 4/3.

Еще одно преимущество AM5, которое мы видим на блок-схеме, — это наличие двух портов USB 3.2 20 Гбит/с.

Редактор: AndreyEx