Что такое многоуровневые кэши?

В постоянно меняющемся ландшафте компьютерной архитектуры стремление оптимизировать иерархию памяти и повысить эффективность обработки привело к появлению усовершенствованных конструкций кэшей. Среди них концепция многоуровневых кэшей выделяется как ключевое новшество. Многоуровневые кэши, или иерархическое кэширование, представляют собой многоуровневый подход к управлению памятью, использующий несколько уровней кэша для преодоления разрыва между высокоскоростными, но ограниченными по емкости кэшами и большей, но медленной основной памятью. В этой статье рассматриваются тонкости многоуровневых кэшей, исследуется их архитектура, преимущества, компромиссы и их роль в современных вычислительных системах. Разбираясь в нюансах многоуровневых кэшей, читатели получают представление о том, как эти сложные структуры памяти способствуют оптимизации производительности, обеспечивая более быстрый и эффективный доступ к данным в современных процессорах. Давайте обсудим, что такое многоуровневые кэши.

Что такое многоуровневые кэши?

Многоуровневые кэши, также известные как иерархические кэши, представляют собой сложный подход к управлению памятью в компьютерной архитектуре. Они предполагают интеграцию нескольких уровней кэша с различными размерами, скоростями и близостью к процессору. Основная цель многоуровневых кэшей — оптимизировать компромисс между скоростью доступа к памяти и емкостью хранилища, что приводит к повышению общей производительности системы.

Использование многоуровневых кэшей представляет собой стратегию, направленную на повышение производительности кэша за счет смягчения последствий «ШТРАФА за ПРОМАХ». Этот термин обозначает дополнительное время, необходимое для передачи данных из основной памяти в кэш всякий раз, когда происходит «промах» кэша.

Чтобы обеспечить более четкое понимание, давайте углубимся в иллюстративный сценарий, включающий 10 ссылок на память для получения требуемой информации. Этот сценарий будет рассмотрен в контексте трех различных примеров проектирования системы:

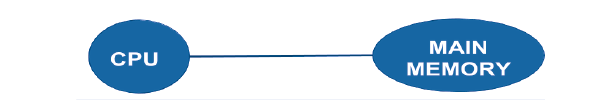

Пример 1: Проектирование системы без кэш-памяти

В этом сценарии центральный процессор устанавливает прямую связь с основной памятью, минуя любое задействование кэшей. Следовательно, центральный процессор вынужден 10 раз взаимодействовать с основной памятью для извлечения целевой информации.

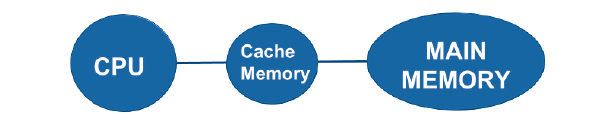

Пример 2: Проектирование системы с использованием кэш-памяти

В этом сценарии центральный процессор инициирует начальную оценку, чтобы определить наличие желаемых данных в кэш-памяти. Это включает проверку того, происходит ли «попадание» или «промах» в кэше. Если, например, имеется три экземпляра кэша «miss», доступ к основной памяти будет осуществлен только три раза. Очевидно, что в этом контексте штраф за промах сокращается, поскольку к основной памяти обращается меньше пользователей по сравнению с предыдущим сценарием.

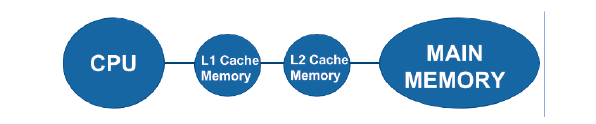

Пример 3: Проектирование системы с многоуровневой кэш-памятью

В этом контексте повышение производительности кэша является еще одним шагом вперед за счет реализации многоуровневых кэшей. Как показано на диаграмме выше, мы изучаем двухуровневую конструкцию кэша. Если, например, в кэш-памяти L1 происходит три «промаха» кэша, а в пределах них два «промаха» происходят в кэш-памяти L2, основная память задействуется только дважды. Очевидно, что штраф за промах существенно снижен по сравнению с предыдущим сценарием, что значительно повышает общую производительность кэш-памяти.

Примечание: Изучив вышеупомянутые три сценария, становится очевидным, что наша цель — уменьшить количество ссылок на основную память, эффективно снизив штраф за пропуск для повышения производительности целостной системы. Примечательно, что в рамках многоуровневого проектирования кешей кэш L1 напрямую связан с центральным процессором, отличается компактным размером и быстрой реакцией. С другой стороны, кэш L2 подключен к основному кэшу, который является кэшем L1. Хотя кэш L2 обладает большей емкостью и работает сравнительно медленнее, он остается быстрее основной памяти.

Эффективное время доступа = Частота обращений * Время доступа к кэшу + Частота пропусков * Меньшее время доступа к уровню

Среднее время доступа к многоуровневому кэшу: (Tavg)

Tavg = H1 C1 + (1 – H1) (H2 C2 +(1 – H2) M )

где:

- H1 — частота обращений в кэшах L1.

- H2 — частота обращений в кэше L2.

- C1 — время доступа к информации в кэшах L1.

- C2 — штраф за пропуск при передаче информации из кэша L2 в кэш L1.

- M — это штраф за пропуск при передаче информации из основной памяти в кэш L2.

Преимущества многоуровневых кэшей:

- Повышенная производительность: Многоуровневые кэши значительно повышают общую производительность системы за счет сокращения задержек при доступе к памяти. Близость кэшей к процессору позволяет быстрее извлекать часто используемые данные, ускоряя выполнение программы.

- Оптимизированная иерархия: Многоуровневые кэши поддерживают различные схемы доступа, используя принципы пространственной и временной локализации. Этот иерархический подход гарантирует эффективное управление данными на разных уровнях кэша, максимизируя повторное использование данных.

- Эффективная иерархия памяти: Обеспечивая баланс между размером кэша и скоростью доступа, многоуровневые кэши способствуют более эффективной иерархии памяти. Они позволяют процессорам быстро получать доступ к часто используемым данным, не полагаясь исключительно на более медленную основную память.

- Меньший штраф за промах: Многоуровневые кэши сводят к минимуму влияние «промахов» кэша. Данные, не найденные в кэшах более высокого уровня, все равно могут быть доступны в кэшах более низкого уровня, что уменьшает необходимость доступа к основной памяти и тем самым снижает штраф за пропуск.

- Универсальность: Многоуровневые кэши могут быть адаптированы к различным вычислительным системам и архитектурам, обеспечивая повышенную производительность на широком спектре устройств, от ноутбуков и настольных компьютеров до серверов и мобильных устройств.

Недостатки многоуровневых кэшей

- Сложность: Внедрение многоуровневых кэшей и управление ими вносит повышенную сложность в структуру иерархии памяти. Эта сложность может усложнить управление кэшем и потребовать сложных политик замены кэша.

- Стоимость: Многоуровневые кэши требуют дополнительного места на чипе, что может повысить производственные затраты. Включение нескольких уровней кэша требует большего количества аппаратных ресурсов, что влияет на производственные затраты.

- Компромисс во времени доступа: В то время как кэши более высокого уровня обеспечивают более быстрое время доступа, кэши более низкого уровня могут иметь несколько более длительное время доступа из-за их больших размеров. Решающее значение имеет баланс между временем доступа и пропускной способностью.

- Ограниченное улучшение: Несмотря на преимущества, многоуровневые кэши могут не обеспечить существенных улучшений для приложений с нерегулярными схемами доступа к памяти или для задач, требующих больших рабочих наборов, превышающих емкость кэша.

Применение многоуровневых кэшей:

- Общие сведения о вычислениях: Многоуровневые кэши широко используются в настольных компьютерах, ноутбуках и мобильных устройствах для ускорения работы повседневных приложений и повышения общей отзывчивости пользовательских интерфейсов.

- Серверы: Серверы, особенно те, на которых размещены базы данных и которые обслуживают несколько клиентов, выигрывают от многоуровневых кэшей. Иерархия помогает сократить время запросов к базе данных и повышает эффективность поиска данных.

- Высокопроизводительные вычисления: В суперкомпьютерах и кластерах, используемых для научного моделирования и исследований, многоуровневые кэши используются для оптимизации производительности и ускорения сложных вычислений.

- Встроенные системы: Многоуровневые кэши используются во встроенных системах, включая устройства Интернета Вещей и автомобильную электронику, для обеспечения баланса между скоростью обработки данных и энергопотреблением.

- Игровые консоли: Игровые консоли используют многоуровневые кэши для увеличения времени загрузки игровых ресурсов, сокращения задержек и обеспечения бесперебойного игрового процесса.

- Обработка графики: Графические процессоры также используют многоуровневые кэши для оптимизации доступа к текстурам и данным вершин, что крайне важно для рендеринга графики в приложениях реального времени.

Заключение

В стремлении повысить скорость вычислений и эффективность многоуровневые кэши становятся жизненно важным архитектурным новшеством. Эти иерархические структуры памяти обеспечивают тонкий баланс между емкостью и скоростью, позволяя процессорам быстро извлекать часто используемые данные при минимизации задержек. Поскольку технологии продолжают развиваться, многоуровневые кэши остаются краеугольным камнем современных вычислений, оптимизируя иерархию памяти для обеспечения бесперебойного и гибкого выполнения приложений на широком спектре устройств. Понимание значения многоуровневых кэшей необходимо для понимания тонкостей современных процессоров и их роли в предоставлении мощных и эффективных вычислительных возможностей.

Часто задаваемые вопросы по многоуровневым кэшам

Вот несколько часто задаваемых вопросов по многоуровневым кэшам.

Вопрос 1: Какова цель многоуровневых кэшей?

Многоуровневые кэши предназначены для устранения разрыва между высокоскоростными, но ограниченными по емкости кэшами и более крупной, но медленной основной памятью. Они оптимизируют иерархию памяти, обеспечивая многоуровневый подход к хранению данных, повышая скорость доступа к данным и общую производительность системы.

Вопрос 2: Как многоуровневые кэши организованы с точки зрения иерархии?

Многоуровневые кэши организованы иерархически, обычно состоящие из нескольких уровней, таких как кэши L1, L2 и иногда L3. Эти уровни распределяются в зависимости от близости к процессору: кэши более высокого уровня расположены ближе к процессору, а кэши более низкого уровня — дальше.

Вопрос 3: Как многоуровневые кэши способствуют повышению производительности?

Многоуровневые кэши хранят часто используемые данные ближе к процессору, уменьшая задержку доступа к памяти. Такая близость приводит к более быстрому извлечению данных, что повышает скорость выполнения программ и общую производительность системы.

Вопрос 4: Поддерживают ли многоуровневые кэши различные схемы доступа?

Да, многоуровневые кэши предназначены для оптимизации производительности при различных шаблонах доступа. Кэши более высокого уровня, такие как L1, оптимизированы для временной локализации (повторное использование недавно полученных данных), в то время как кэши более низкого уровня, такие как L2 или L3, обрабатывают большие фрагменты данных и обслуживают пространственную локализацию (доступ к соседним данным).

Вопрос 5: Есть ли какие-либо недостатки в использовании многоуровневых кэшей?

Хотя многоуровневые кэши обеспечивают преимущества в производительности, они сопряжены с компромиссами, такими как повышенная сложность управления кэшем и проектирования иерархии памяти. Кроме того, в то время как кэши более высокого уровня уменьшают задержку, кэши более низкого уровня или обращения к основной памяти могут приводить к более высокой задержке.

Вопрос 6: Как многоуровневые кэши влияют на стоимость процессоров?

Многоуровневые кэши увеличивают общие требования к пространству микросхемы, что может привести к увеличению производственных затрат. Включение нескольких уровней кэша требует дополнительных аппаратных ресурсов и может повлиять на производственный процесс.

Вопрос 7: Можно ли найти многоуровневые кэши во всех типах вычислительных устройств?

Да, многоуровневые кэши используются в различных типах вычислительных устройств, включая настольные компьютеры, ноутбуки, серверы и даже мобильные устройства. Они играют решающую роль в оптимизации иерархии памяти и повышении эффективности доступа к данным в современных процессорах.

Редактор: AndreyEx