Подробный обзор AMD Epyc 7003 Milan-X с 3D V-Cache

Применяя новый подход к максимальному повышению производительности серверных процессоров для некоторых ресурсоемких приложений, в ноябре 2021 года AMD анонсировала версии Epyc 7003 Series с расширенным кешем L3 предоставить более полное представление о том, как и почему AMD решила пойти по этому пути.

Напомним, что обычные серверные процессоры Epyc третьего поколения используют архитектуру Zen 3 и вмещают до 64 ядер и 128 потоков. Каждое ядро несет 64 КБ кэш-памяти L1 и 512 КБ кэш-памяти L2, и в этом отношении ничего не меняется.

Все достоинства Milan-X сосредоточены на увеличении площади L3 в три раза. Причина этого, по словам AMD, заключается в том, чтобы позволить различным рабочим нагрузкам технических вычислений, которые, как правило, имеют большие требования к оперативной памяти, помещаться во встроенный кэш, а не загружаться из гораздо более медленной основной памяти. Это значительно повышает производительность для определенных приложений, требующих большого объема кеша, но, будучи беспристрастным, этот подход граничит с бессмысленностью, если рабочая нагрузка связана с вычислениями, а не с кешем.

Чтобы было ясно, Milan-X предназначен для обслуживания относительно нишевой аудитории, которая неявно понимает характеристики узких мест рабочей нагрузки и определяет кэш-память на кристалле в качестве основного препятствия.

AMD предлагает прекрасную возможность использовать дополнительный L3 на том же узле процесса, если это возможно, потому что сверхплотная SRAM — транзисторный строительный блок для кэшей — плохо масштабируется с итеративным сжатием кристалла. Судя по приведенной выше графике, поставляемой AMD, площадь памяти SRAM практически не уменьшается при переходе с 5 нм, скажем, на 3 нм.

Это понимание объясняет, почему AMD решила улучшить текущий кэш L3 новым способом для конкретных рабочих нагрузок, и мы покажем интересные цифры ниже. Следующий вопрос — как, потому что если добавление кэша L3 является благом для IPC, почему этого не сделали раньше?

Zen 3 создан для стекирования кеша

Простейшая причина, по которой не добавляются дополнительные кучи L3, связана с увеличенными размерами кристалла и связанной с этим сложностью разводки. Конечно, AMD и Intel могли раньше удвоить кэш-память, но это привело бы к увеличению площади кремния на кристалл до экономически и термически неприемлемого уровня. Вот почему мы раньше не видели Epyc или Xeon с 1 ГБ L3.

Что необходимо, так это способ сохранить текущую площадь кремния и разместить дополнительный L3 поверх, каким-то образом, не уменьшая пропускную способность и сводя к минимуму дополнительную задержку доступа. Сложный заказ. Войдите в 3D V-Cache Milan-X.

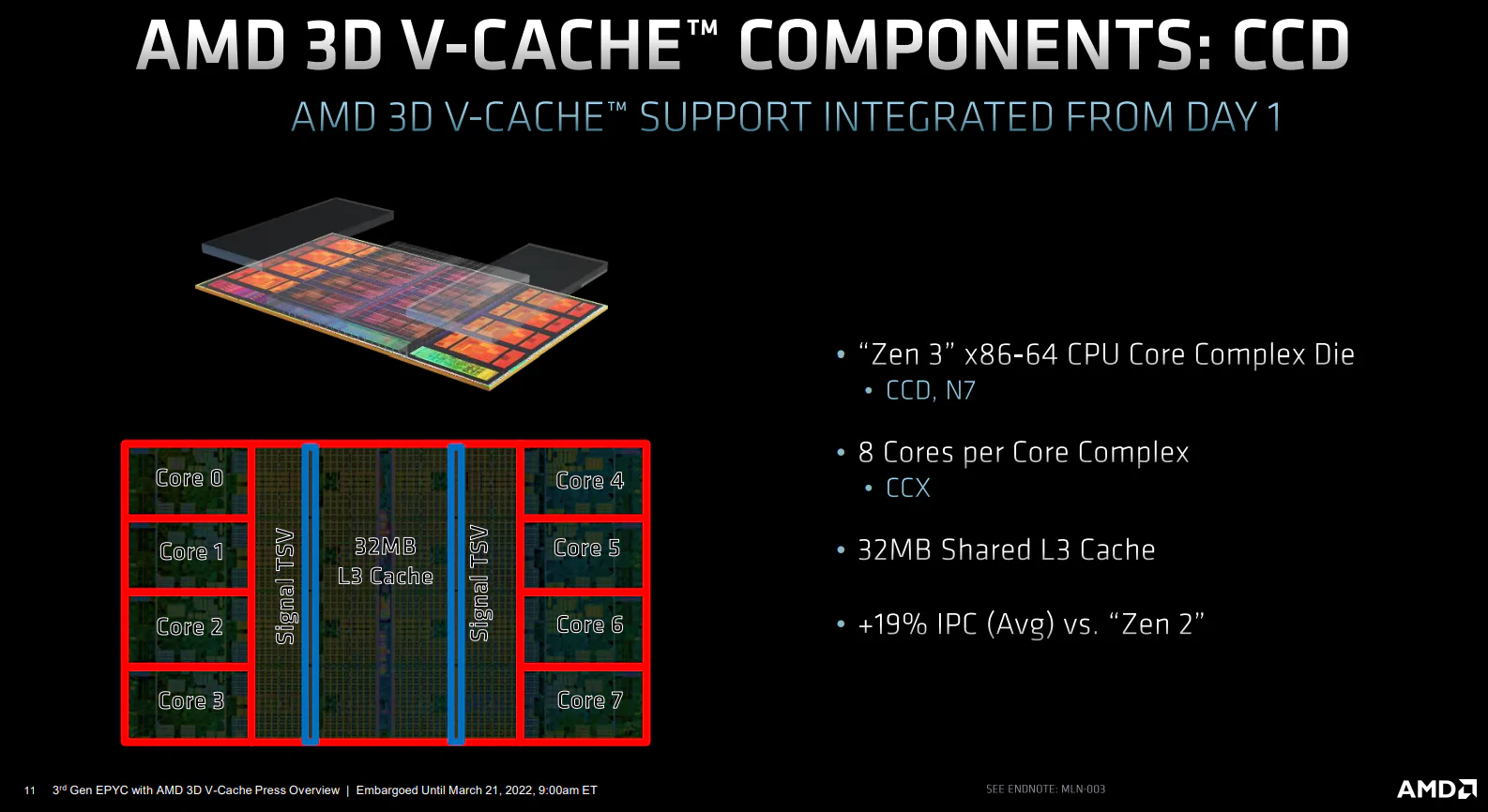

Выше показан высокоуровневый одноядерный сложный кристалл (CCD) от Epyc Milan. Построенный на 7-нанометровом техпроцессе от партнера TSMC, компоновка сразу знакома. Каждое из восьми ядер имеет доступ к 32 МБ L3, и восемь из этих комплексов связаны вместе, чтобы сформировать головной чип 64C128T. AMD говорит, что ПЗС-матрица Zen 3 была специально создана с учетом перспективного 3D V-Cache, и мы знаем это, потому что она имеет необходимые крючки из меди через кремний через (TSV), предназначенные для добавления кристаллов сверху.

Дополнительный кеш отображается как один блок

Компания AMD, разработанная совместно с TSMC, использует технику, известную как гибридное связывание, для обеспечения неограниченной пропускной способности из стекированного L3. Названный Сэмом Наффзигером, корпоративным сотрудником AMD, «прорывной возможностью», прямая гидрофильная связь химически сплавляет диоксид кремния на существующем L3 и многослойном X3D. Гибридное название, представляющее как химические, так и металлургические связи, происходит от соединения меди с медью, как показано слева.

Такой подход обеспечивает сверхплотные межсоединения между уровнями, благодаря чему стекированный кэш ведет себя как существующий L3. Это возможно, поскольку базовые 32 МБ L3 содержат достаточно плотную проводку и контроллер кольцевой шины для обслуживания любого стекированного кэша. Другими словами, AMD думала о 3D V-Cache с первого дня; его нельзя задним числом перенести на другие чипы, не поддерживающие передачу TSV.

Два 32-мегабайтных стека L3 укладываются поверх существующего L3 путем соединения через 9-микронные TSV-шаги на 13-м слое верхнего кристалла. Если подумать, X3D в два раза плотнее существующего базового L3 для той же области — внизу, помните, что по 16 МБ с каждой стороны — и это возможно, потому что X3D — это плотный кэш с меньшим энергопотреблением; нет логики управления или кольцевой шины, о которых нужно думать.

Ядра и, соответственно, операционная система не обращают внимания на связывание дополнительного L3. Milan-X выглядит и в значительной степени работает как монстр L3 с тройной плотностью. Мы говорим «в основном», так как при доступе к верхнему кешу возникают незначительные накладные расходы в четыре цикла, но это довольно хороший результат, учитывая все обстоятельства.

Другой вид на Милан (слева) и Милан-X (справа) CCD показывает, что происходит. Как объяснялось ранее, с левой стороны все то же самое; отличается только кеш L3. Теперь вместо 32 МБ на ПЗС у нас 96 МБ отображаются как один блок, хотя на самом деле это два объединенных вместе блока.

Могла ли AMD использовать Milan-X для значительного увеличения L1 и L2? Вероятно, но поскольку клиенты настраивают свои рабочие нагрузки на базовую архитектуру и требуют согласованности приложений, возиться только с L3 — безопасная ставка.

Модели AMD Epyc Milan-X

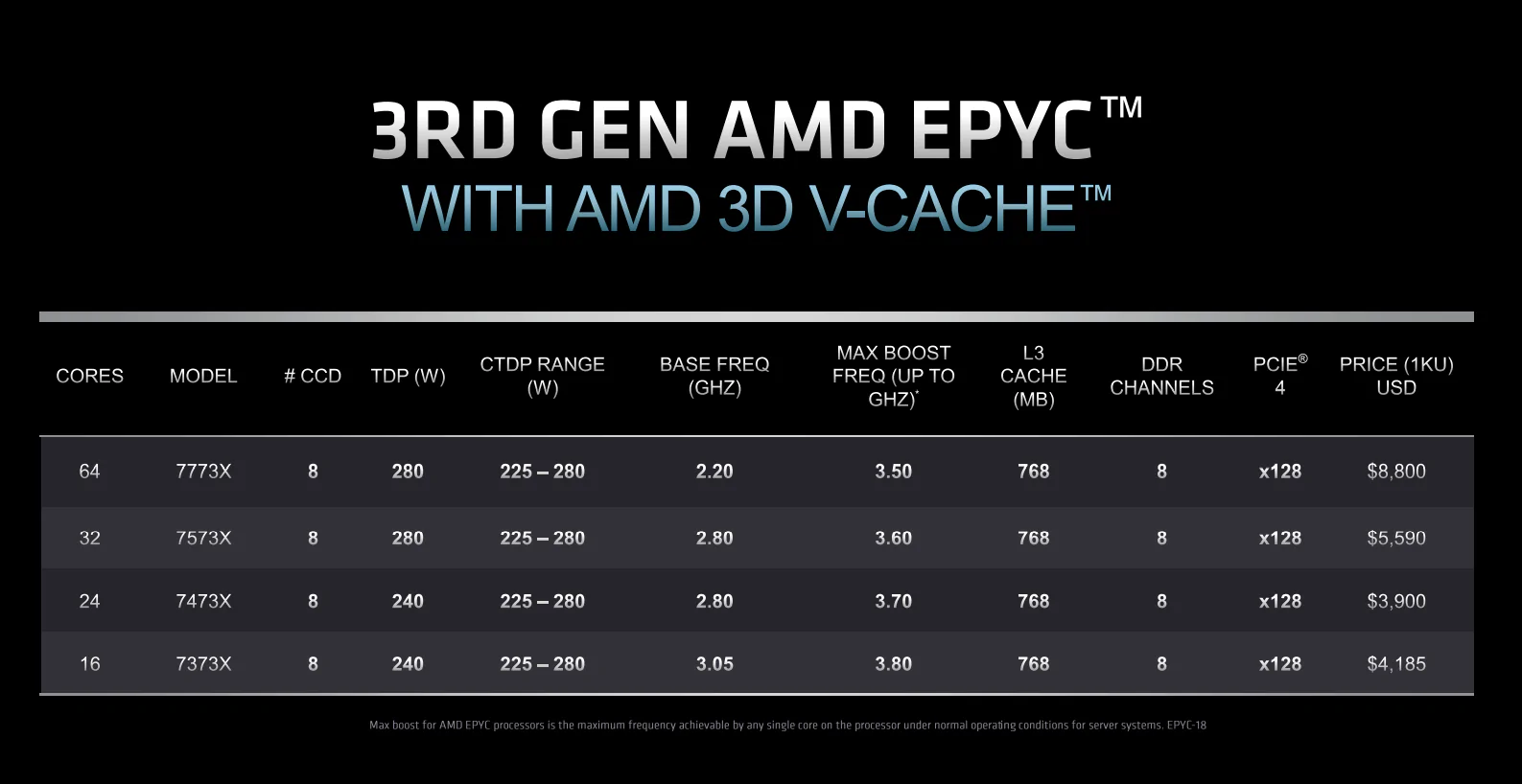

Сегодня AMD официально выпускает четыре чипа с 3D V-Cache. Квартет имеет суффикс X, обозначающий утроение L3, и, что интересно, все они созданы из лучших в своем классе установок с 8 ПЗС, что приводит к 768 МБ для всех. Например, 16-ядерный 7373X имеет только два активных ядра в каждой 8-ядерной ПЗС, 24-ядерный — три и так далее.

Milan-X организован таким образом, чтобы максимизировать L3 на ядро, что является смыслом его существования. В качестве крайнего примера, два ядра 7373X на ПЗС-матрицу имеют доступ к 96 МБ L3 или 48 МБ каждое, хотя это не работает таким образом, поскольку каждое ядро в ПЗС-матрице имеет полный доступ ко всем 96 МБ. Соотношение снижается до 12 МБ на ядро для 7773X, но это все равно впечатляет.

По сравнению с решениями, отличными от X, которые рекламируют те же конфигурации ядра, чипы 3D V-Cache примерно на 20% дороже. Энергопотребление остается примерно на том же уровне, так как дополнительная мощность, необходимая для работы с дополнительными 512 МБ памяти L3, компенсируется большим числом обращений к кэш-памяти, что означает меньшую потребность в питании внешней памяти DDR4 так часто.

Любопытно, что 16-ядерный 7373X дороже 24-ядерного 7473X — то же самое и при сравнении не-X 73F3 (16C32T) с 7473 (24C48T). Это может быть связано с приложениями, лицензируемыми на основе количества ядер, и AMD знает, что может взимать дополнительную плату при использовании программного обеспечения, которое поддерживает 16 ядер.

Установка Milan-X на существующие платы, поддерживающие Epyc Milan, — это просто обновление BIOS. По словам AMD, наибольший прирост производительности чипов с большим объемом кэш-памяти достигается в рабочих нагрузках EDA, CFD, конечных элементов и структурного анализа.

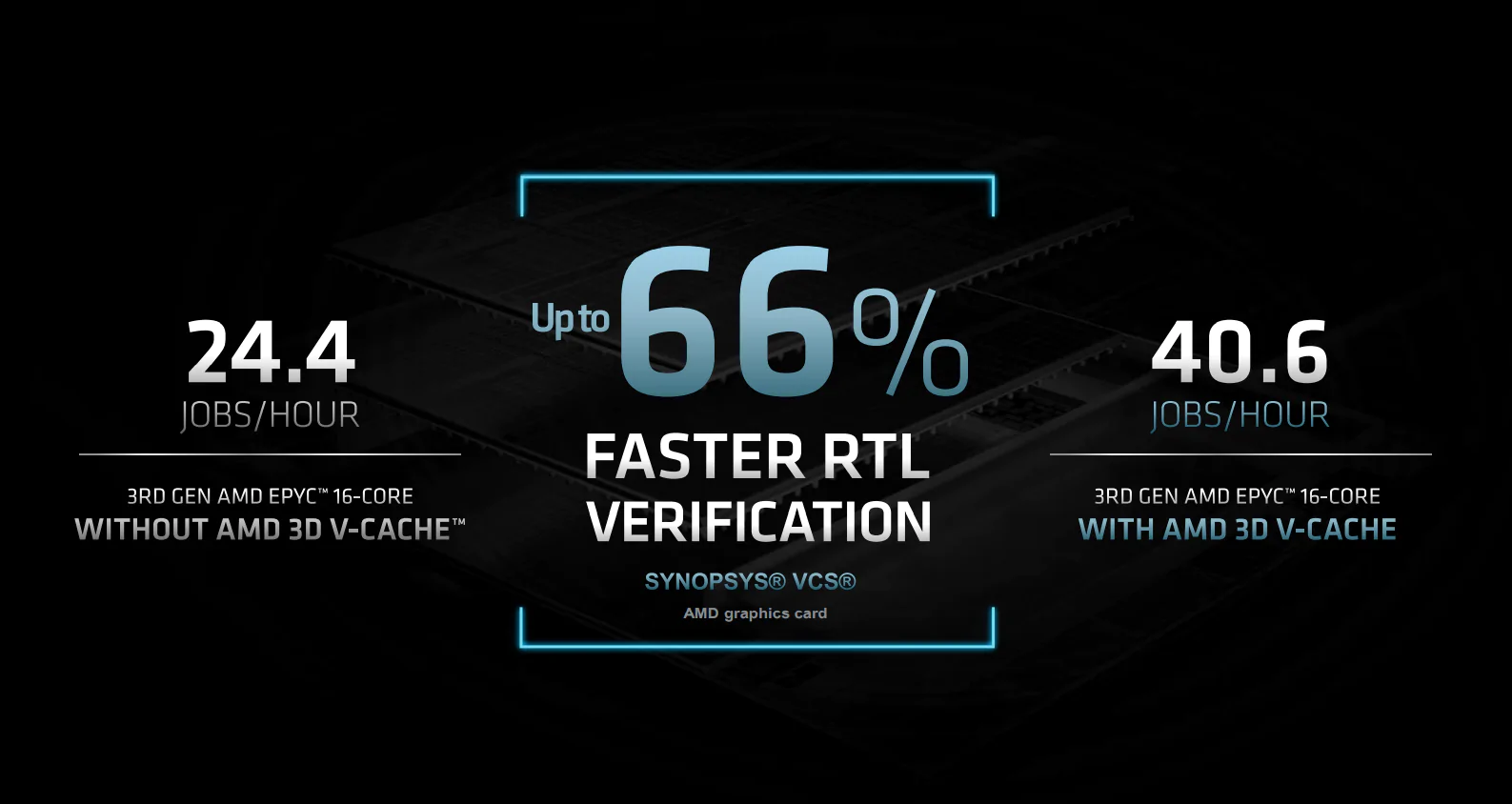

Компания сдержанно сравнивает Milan X с обычным Milan, за исключением одного теста, где Milan-X на 66% быстрее, чем Milan с тем же ядром в проверке RTL. Пробег повышения производительности значительно варьируется в зависимости от приложения, и крупные клиенты какое-то время тестировали Milan-X, точно зная, как он сравнивается с обычным Milan для своих вариантов использования.

Обертка

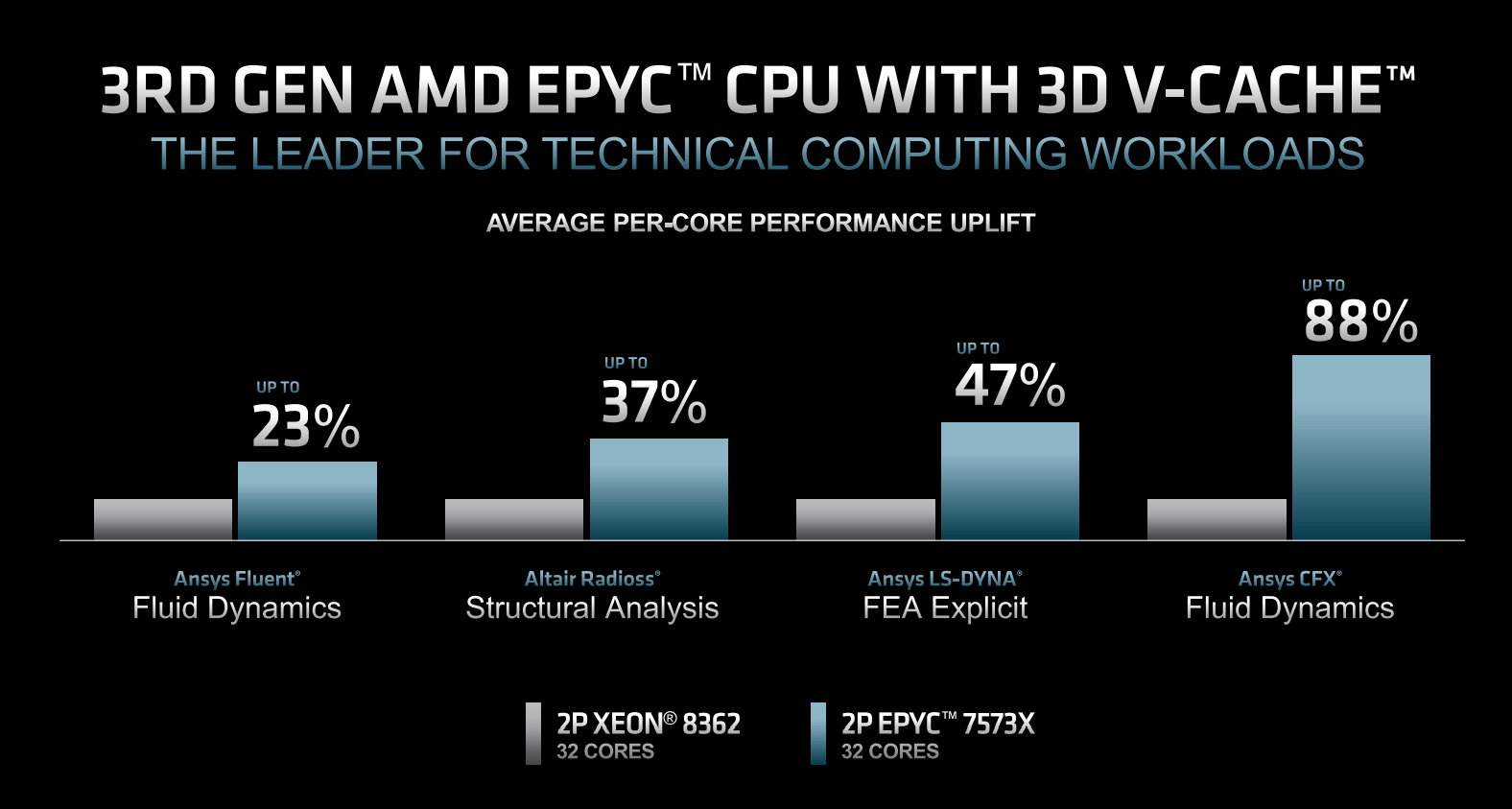

По сравнению с процессорами Intel Xeon Platinum (Ice Lake) по принципу «ядро-ядро» AMD выбирает чувствительные к кэш-памяти тесты, в которых она очень хорошо справляется. Наблюдатели отрасли знают, что Intel собирается выпустить процессоры Sapphire Rapids Xeon следующего поколения в ближайшее время, поэтому выше comparo устареет в ближайшее время. Тем не менее, мы ожидаем, что AMD сохранит лидерство во многих приложениях.

Разработанный для удобного размещения внутри кластеров локальных серверов, где масштабирование рабочей нагрузки является почти линейным и чувствительным к уровням кэша, Milan-X имеет смысл для небольшой, но богатой по объему части заказчиков серверов. Большинство других прекрасно справятся с действующим Миланом, особенно если рабочие нагрузки в большей степени связаны с вычислениями, и, вероятно, подождут, пока Genoa на базе Zen 4 не наберет обороты в конце этого года.

AMD Epyc Milan-X, выступающий в качестве передового процессора с вертикальным размещением большого количества дополнительной кэш-памяти L3 для значительного выигрыша в зависимости от рабочей нагрузки, реализуя до 1,5 ГБ на плату 2P, является убедительным доказательством концепции.

Редактор: AndreyEx