В компьютерной архитектуре, где инновации стимулируют технический прогресс, появление RISC-V вызвало революцию. RISC-V, архитектура набора команд с открытым исходным кодом (ISA), является эталоном гибкости, модульности и доступности, меняющим ландшафт проектирования процессоров и подпитывающим устремления самых разных отраслей промышленности. Эта статья посвящена миру RISC-V, исследуя его происхождение, принципы, преимущества и потенциал для формирования будущего вычислительной техники.

Взгляд на истоки RISC-V

RISC-V, произносящийся как «RISC Five», уходит своими корнями в Калифорнийский университет в Беркли, где он появился на свет в 2010 году. Команда под руководством профессора Крсте Асановича приступила к разработке архитектуры набора инструкций с открытым исходным кодом, которая освободила бы от ограничений, связанных с проприетарными разработками, открыв новую эру инноваций и сотрудничества. Название проекта «RISC-V» означает его наследие как архитектуры «RISC» (компьютер с сокращенным набором команд), в то время как «V» представляет пятую основную версию проекта команды.

Основы RISC-V

По своей сути RISC-V воплощает в себе простоту и модульность. В отличие от проприетарных ISA, которые тщательно охраняются и часто требуют лицензионных сборов, RISC-V открыт и находится в свободном доступе. Его модульная конструкция позволяет разработчикам выбирать и внедрять только те инструкции, которые имеют отношение к их конкретному применению, сводя к минимуму ненужную сложность. Такая модульность не только повышает эффективность, но и расширяет возможности настройки, делая RISC-V адаптируемым к широкому спектру вариантов использования.

Основные характеристики и преимущества RISC-V

1. Открытость и доступность: открытый исходный код RISC-V поощряет сотрудничество и инновации в академических кругах, исследованиях и промышленности. Он демократизирует доступ к разработке процессоров, позволяя стартапам, исследователям и любителям экспериментировать и творить без барьеров.

2. Модульность и гибкость: Модульная архитектура RISC-V позволяет разработчикам создавать процессоры, адаптированные к конкретным рабочим нагрузкам. Такая адаптивность особенно выгодна во встраиваемых системах, устройствах Интернета вещей (IoT) и сценариях периферийных вычислений.

3. Масштабируемость: RISC-V обеспечивает масштабируемость от микроконтроллеров до высокопроизводительных серверных процессоров. Такая масштабируемость делает его привлекательным выбором для широкого спектра приложений, от носимых устройств с низким энергопотреблением до суперкомпьютеров.

4. Снижение сложности проектирования: Благодаря упрощенному набору команд RISC-V упрощает проектирование и верификацию процессора, что потенциально приводит к ускорению циклов разработки и снижению производственных затрат.

5. Инновации и исследования: Открытый характер RISC-V создает благодатную почву для исследований и экспериментов в области компьютерной архитектуры, позволяя изучать новые идеи без ограничений, связанных с несвободными лицензиями.

6. Рост экосистемы: Экосистема RISC-V быстро расширяется, и различные компании, включая известных игроков и стартапы, разрабатывают продукты, инструменты и сервисы на основе RISC-V.

Понимание архитектуры RISC-V

RISC-V (произносится «RISC Five») — это архитектура набора команд со свободным исходным кодом (ISA), которая спроектирована так, чтобы быть простой, модульной и расширяемой. В отличие от проприетарных ISA, RISC-V не привязан к конкретной компании или поставщику, что делает его очень универсальным и адаптируемым к широкому спектру приложений. Его архитектура построена на нескольких ключевых принципах:

1. Сокращенный набор команд: RISC-V придерживается философии архитектуры с сокращенным набором команд, или RISC. Это означает, что его набор команд намеренно сведен к минимуму, сосредоточив внимание на небольшом наборе простых инструкций, которые могут быть быстро выполнены. Простота инструкций способствует более быстрому выполнению и упрощению дизайна.

2. Модульность: Одной из выдающихся особенностей RISC-V является его модульная конструкция. Архитектура предоставляет базовый набор инструкций, и дополнительные необязательные расширения инструкций могут быть добавлены по мере необходимости для конкретных приложений. Такая модульность позволяет разработчикам системы адаптировать набор команд в соответствии с требованиями их целевых приложений.

3. 32-разрядные и 64-разрядные варианты: RISC-V предлагает как 32-разрядные, так и 64-разрядные варианты, обеспечивая гибкость при удовлетворении различных вычислительных потребностей. 32-разрядная версия подходит для встраиваемых систем с низким энергопотреблением и микроконтроллеров, в то время как 64-разрядная версия предназначена для высокопроизводительных вычислительных сред.

4. Архитектура Load-Store: RISC-V соответствует архитектуре load-store, что означает, что арифметические и логические операции выполняются только над данными, загруженными из памяти, а затем сохраненными обратно. Такой подход упрощает набор команд и повышает эффективность операций с памятью.

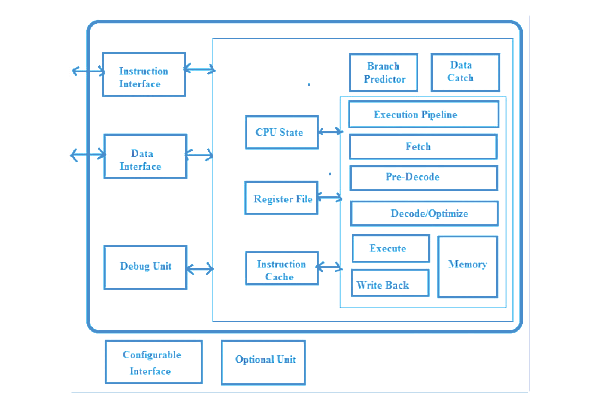

Работа RISC-V

Работу процессора RISC-V можно разбить на несколько этапов:

1. Выборка инструкции (IF): процессор извлекает инструкцию из памяти, используя программный счетчик (PC) в качестве эталона. Значение PC увеличивается, указывая на следующую инструкцию.

2. Декодирование инструкции (ID): На этом этапе декодируется выбранная команда, чтобы определить операцию, которая должна быть выполнена, и задействованные операнды.

3. Выполнение (ПРИМЕР): выполняется фактическое вычисление или операция, указанные в инструкции. Это может включать арифметические, логические или другие операции.

4. Доступ к памяти (MEM): Если инструкция включает доступ к памяти (например, операции загрузки/сохранения), этот этап отвечает за чтение из памяти или запись в память.

5. Обратная запись (WB): при необходимости результат выполнения записывается обратно в файл register. Этот этап гарантирует, что обновленные данные будут доступны для последующих инструкций.

Проблемы и перспективы RISC-V на будущее

Несмотря на свои обещания, RISC-V сталкивается с трудностями в достижении широкого внедрения и совместимости в различных аппаратных и программных экосистемах. Относительная новизна ISA также означает, что разработчики могут столкнуться с ограничениями в плане доступных инструментов, библиотек и документации по сравнению с более устоявшимися архитектурами.

Однако траектория RISC-V, несомненно, остается восходящей. По мере развития экосистемы эти проблемы, вероятно, уменьшатся, открывая дверь в будущее, где RISC-V играет ключевую роль в формировании компьютерных ландшафтов и расширении возможностей новых рубежей технологического прогресса.

Заключение

RISC-V стал преобразующей силой в мире компьютерной архитектуры, воплощая принципы открытости, модульности и гибкости. Обладая потенциалом стимулирования инноваций, демократизации дизайна процессоров и революционизации различных отраслей промышленности, RISC-V является свидетельством силы совместных усилий с открытым исходным кодом в формировании будущего вычислительной техники. Поскольку RISC-V продолжает набирать обороты, его влияние готово достичь новых высот, оставляя неизгладимый след в постоянно развивающемся технологическом ландшафте.

Часто задаваемые вопросы (FAQs)

Вот некоторые из часто задаваемых вопросов по архитектуре risc-v.

1. Что такое архитектура RISC-V и чем она отличается от других процессорных архитектур?

Архитектура RISC-V — это архитектура набора команд с открытым исходным кодом (ISA), разработанная для процессоров. Он отличается от других архитектур тем, что является модульным и расширяемым, позволяя пользователям адаптировать набор команд к их конкретным требованиям. RISC-V, в отличие от проприетарных ISA, не принадлежит какой-либо одной компании, что делает его открытым и доступным для всех для развития и инноваций.

2. Как RISC-V достигает модульности в своей конструкции?

RISC-V обеспечивает модульность благодаря своему базовому набору команд и дополнительным расширениям команд. Базовый набор предоставляет основные инструкции, в то время как расширения добавляют определенные функциональные возможности. Разработчики могут выбирать и внедрять только необходимые расширения, адаптируя процессор к требованиям своих приложений. Такая модульность способствует эффективности и гибкости проектирования.

3. Каковы преимущества архитектуры хранилища загрузки RISC-V?

Архитектура хранилища загрузки RISC-V упрощает выполнение команд, выполняя арифметические и логические операции исключительно с данными, загруженными из памяти. Такой подход минимизирует сложность команд, сокращает время доступа к памяти и обеспечивает эффективную конвейерную обработку. Он также позволяет улучшить управление иерархией памяти и ее оптимизацию.

4. Как RISC-V обрабатывает как 32-разрядные, так и 64-разрядные варианты?

RISC-V поддерживает как 32-разрядные, так и 64-разрядные варианты для удовлетворения различных вычислительных потребностей. 32-разрядная версия подходит для встраиваемых систем и приложений, где решающее значение имеет энергоэффективность. 64-разрядная версия предназначена для решения более сложных вычислительных задач, таких как высокопроизводительные вычисления, где требуется адресация большего объема памяти и арифметика более высокой точности.

5. Как открытый исходный код архитектуры RISC-V приносит пользу разработчикам и отраслям промышленности?

Открытый исходный код RISC-V расширяет возможности разработчиков и отраслей промышленности во многих отношениях. Он позволяет настраивать дизайн процессоров, поощряя инновации и специализацию для конкретных приложений. Разработчики могут получить доступ к спецификациям архитектуры, сотрудничать и обмениваться знаниями, что приводит к ускорению циклов разработки и улучшению решений. Открытая экосистема также снижает затраты на лицензирование и зависимость от отдельных поставщиков, способствуя здоровой конкуренции и динамичному развитию, ориентированному на сообщества.